Intel高级院士曝光自家10nm工艺:集成度比优于对手

信息来源: http://emcmy.com 时间:2017/1/6 0:51:14

台积电和三星纷纷量产10nm,而曾经作为半导体工艺技术龙头的Intel却动作迟缓,待在14nm上不肯动弹了,10nm目前看最快最快也得2018年下半年。

那么,真的是Intel在技术上黔驴技穷了?

显然不是。Intel在最新一期的半导体行业权威刊物《IEEE Spectrum》上撰文,畅谈了自己的10nm工艺,尤其是在技术、成本方面的巨大优势。

Intel高级院士Mark Bohr表示,Intel 10nm工艺的晶体管密度不但会超过现在的Intel 14nm,还会优于其他公司的10nm,也就是集成度比他们更高,栅极间距将从14nm工艺的70nm缩小到54nm,逻辑单元则缩小46%,这比以往任何一代工艺进化都更激进。

他说:“本代工艺和相关产品要传达的一个重要信息,就是希望能够打消行业对于摩尔定律将死的忧虑。”

Intel在技术上的实力其实根本不用怀疑,那么是不是成本限制了10nm?Mark Bohr也谈到了这一点,明确表示Intel 10nm晶圆的整体成本确实会高于14nm,但是平均到每个晶体管上会更低。

和每一代新工艺一样,10nm也能提高晶体管的运行速度,或者降低能耗,但更重要的显然是后者。

Mark Bohr表示:“这些新工艺的首要目标确实是降低能耗,或者说提高能效,只有这样才能在服务器芯片内加入更多核心,或者在GPU内加入更多执行单元,然后才是降低晶体管成本。”

目前,台积电、GlobalFoundries(AMD)、三星等都在积极筹划7nm,Intel的似乎还很遥远。

Mark Bohr对此表示,如果从10nm过渡到7nm会花更长时间,那么最重要的就是想方设法增强已有技术,每年带来新产品。

这似乎意味着,在未来至少五年左右的时间里,Intel仍会坚持当前的产品研发和发布策略,不会变的太激进。

铁粉芯 8材 HST50-8B

高偏流的情况下,磁芯损耗最低,兼且线性良好,是最好的高频材,也是最贵的材料OD(in/mm) ID(in/mm) HT(in/mm)0.500/12.7 0.303/7.7 0.250/6.35Al: 23 nH ±10%

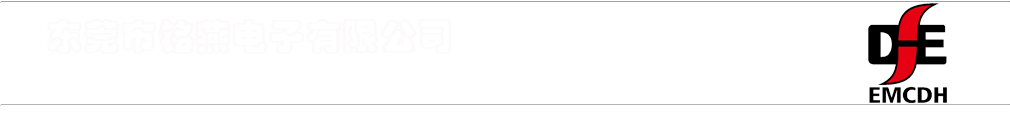

铁粉芯 HST131-52 52材…

52材在高频率下磁芯损耗较低,而磁导率与材料-26相同,在新型的高频抗流器上应用广泛.OD(in/mm) ID(in/mm) HT(in/mm)1.300/33.0 0.640/16.3 0.437/11.1Al: 108 nH ±10% 初…

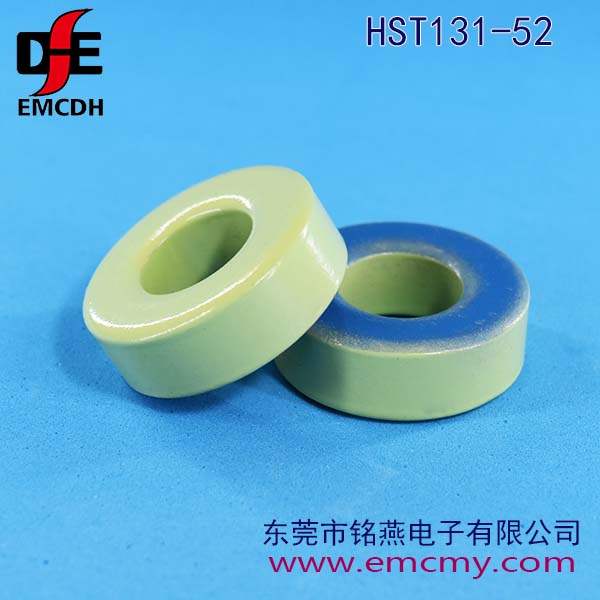

26材 HST157-26

26材最为通行的材料,是一种成本效益最高的一般用途材料,适合功率转换和线路滤波等各种广泛用途. OD(in/mm) ID(in/mm) HT(in/mm)2.000/50.8 1.250/31.8 1.000/25.4Al:…

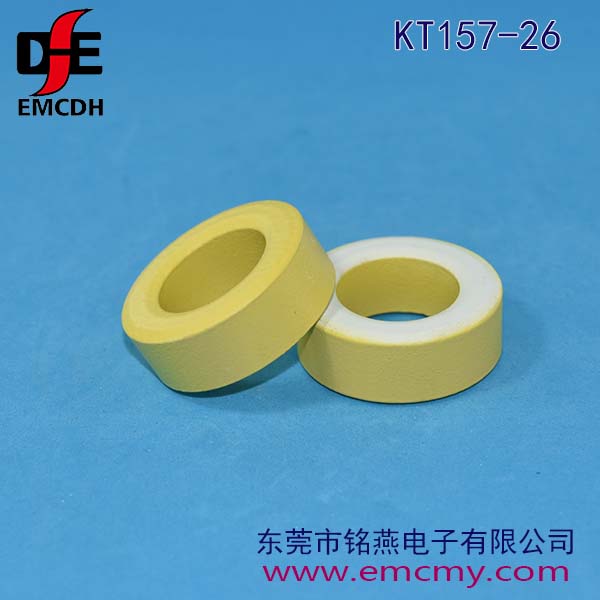

铁粉芯 HST131-52

52材在高频率下磁芯损耗较低,而磁导率与材料-26相同,在新型的高频抗流器上应用广泛.OD(in/mm) ID(in/mm) HT(in/mm)1.300/33.0 0.640/16.3 0.437/11.1Al: 108 nH ±10%

微信

微信